Engineers face a growing dilemma as they strive to design increasingly faster, larger and more complex circuitry into the latest FPGA or ASIC devices within the shortest possible time. Huge, complex designs require the collaboration of several engineers or engineering teams, often belonging to separate companies and distributed in different geographic locations worldwide. This raises the importance of consistent design coding style in order for teams to share code effectively, especially if multiple design flows are in use.

Often these teams will consist of experienced project leaders and designers along with less experienced junior engineers. This makes the need for consistency critical. Moreover, it is imperative that companies carefully scrutinise the planning and creation process for poor design styles, incorrect design rules, and syntax/semantic errors at the earliest possible stage before attempting to simulate or synthesise the design.

Bigger design sizes at higher speeds mean that traditional simulation cycles have become painfully prolonged. Similarly, synthesis can become a protracted and iterative process in order to achieve desired performance goals. Therefore, there is a need to maximise the productivity of potentially long EDA tool runs by ensuring that as many code errors as possible are found and fixed prior to the start of simulation and synthesis.

In order to minimise design times, 80-90% of projects will include re-work of an existing design or re-use of previously designed components or IP, whether internal or purchased. Since this trend is expected to increase, engineers need to ensure the components or subsystems are designed to be re-usable and hence conform to established design re-use rules. Through cooperative efforts in the design community and internal corporate standardisation, re-use methodology guidelines have been developed that can be checked using automated tools.

DesignAnalyst is a new tool from Mentor Graphics designed to detect and isolate a broad range of HDL design problems during the process of design creation. Its fast run-time performance and error isolation capability make it easy for designers to check their code frequently while editing their code and quickly fix the errors they find.

Included with the tool is a rule set based on the industry reference 'Re-use Methodology Manual' to check for a broad range of design errors and adherence to style guidelines. DesignAnalyst also has an easy-to-use interface for building your own rules. You can build rules using a set of parameterised base rules, which allows you to customise your rule sets without any programming. The advantage is that instead of searching through thousands of static rules, you can search for a matching base rule, adjust the parameters to suit your needs, and move to the next rule.

Some examples of rules that the tool enforces are:

* No extra or unused signals.

* Isolate or avoid gated clocks.

* Avoid internally-generated resets.

* Avoid mixed clock edges.

* No multiply-driven signals.

* Assign a value to a signal before reading it.

* Matching comparison/assignment ranges.

* Check for clock boundary crossing and synchronisation.

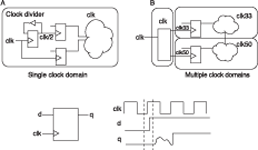

In today's complex designs, multiple clock domains are increasingly common, so this category of checks is one that designers most often request. Figure 2 illustrates a multiple clock domain design (B) vs a single clock domain design (A). The timing diagram below the schematics shows the resulting timing diagram that metastability effects can cause if the clock domains are not properly synchronised.

Conclusion

In order to minimise design-to-production timescales, it is important that potential downstream problems can be identified as early in the design process as possible. Design iterations late in the design cycle can potentially cost several days. Designers today cannot afford to wait until the simulation or synthesis stages of the design process to find problems that could be identified during design entry. DesignAnalyst is a low-cost, configurable HDL design checker that can find and isolate several classes of design errors and dramatically reduce overall design time for complex FPGA and ASIC designs.

| Tel: | +27 11 315 8316 |

| Email: | [email protected] |

| www: | www.asic.co.za |

| Articles: | More information and articles about ASIC Design Services |

© Technews Publishing (Pty) Ltd | All Rights Reserved